Base Development Board FPGA Project¶

Overview¶

----

This project is a base project that was made to test some of the interfaces of the MitySOM 5CSX-H6-42A-RC (Production silicon), which device type 5CSXFC6C6U23C7. Its main features are using the Full HSMC connector as single ended I/O, connecting the FPGA DDR to the HPS memory map, and performing a memory test of the HPS DDR from the FPGA.

- Removing the FPGA DDR controller and Clock Crossing bridge, which also requires removal of the FPGA DDR signals.

- For 5CSX-H6-42A-RC-X, the device type is 5CSXFC6C6U23C8ES.

Updates¶

5/2/2014

- Initial Release

Design Specification¶

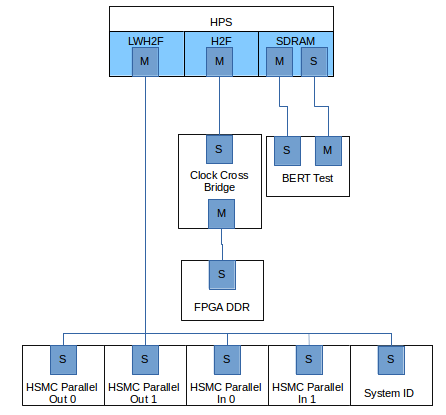

The following design was created using Quartus II version 13.1.4 using the following IP blocks:

- Hard Processor System

- Altera PLL

- System ID Peripheral

- PIO (Parallel I/O)

- Merlin Reset Controller

- Avalon-MM Pipeline Bridge

- Modular SGDMA dispatcher

- Modular SGDMA read master

- Modular SGDMA write master

- Altera Avalon Data Pattern Generator

- Altera Avalon Data Pattern Checker

- Clock Source

High Level System Overview¶

Features¶

This project contains the following features:

- Full HSMC connector setup for single ended I/O

- Access to FPGA DDR from HPS memory map

- HPS DDR test from FPGA fabric

Downloads¶

Go to top