Configuration¶

- FPGA configuration will be from HPS, PCIe, or SPI. QSPI is not be supported, since QSPI is used for the HPS.

- FPGA configuration could also be from the FPP

- If RGMII is not used on the HPS pins

- Fastest configuration scheme

- BSEL, CSEL and MSEL lines are brought out to the edge connector.

- EPCS and EPCQ are supported using DATA0-DATA4, DCLK. These pins come out to the header.

- HPS boot can be from FPGA (PCIe), QSPI (NOR), or SD/MMC.

Boot Pin Options¶

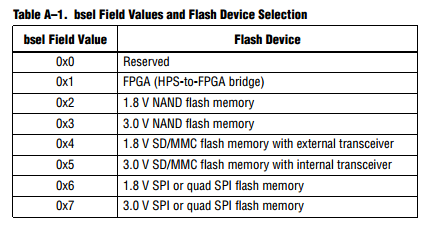

For booting the HPS, the BSEL and CSEL pins are detailed in: CV-5400A

BSEL Options¶

- 001 - FPGA

- 010 - 1.8V NAND

- 101 - 3V SD/MMC

- 110 - 1.8V SPI or QSPI (48MB, 32MB and 16MB QSPI NOR)

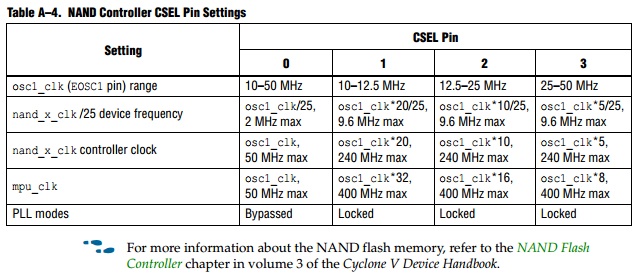

CSEL - NAND¶

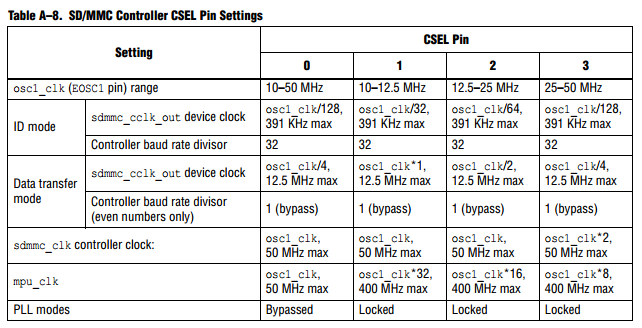

CSEL - SD/MMC¶

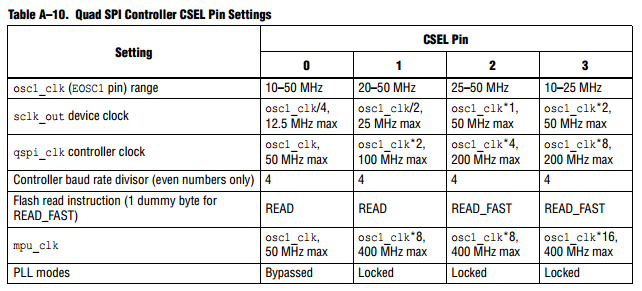

CSEL - QSPI¶

- 00 - PLL Bypassed

We recommend that CSEL be set to '00' to bypass the internal PLL's on boot per the following errata sheet from Altera (https://www.altera.com/ja_JP/pdfs/literature/es/es_cyclone_v.pdf).

======================

FPGA Configuration Schemes¶

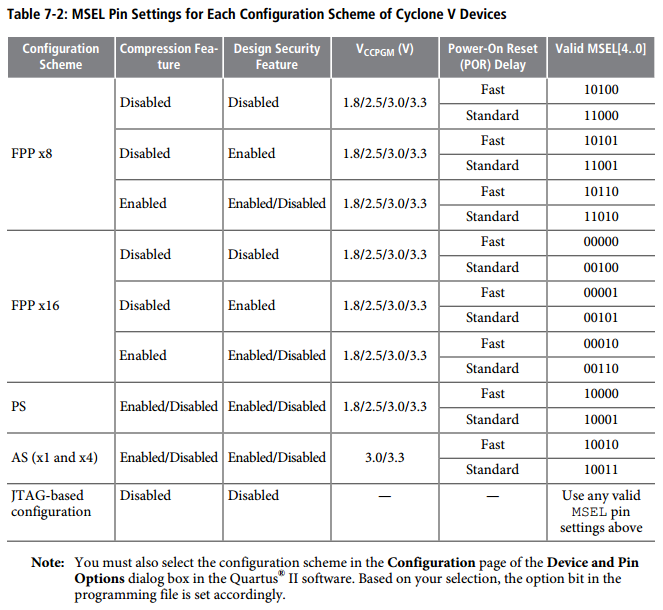

The FPGA boot options include MSEL[4:0] - see CV-52007

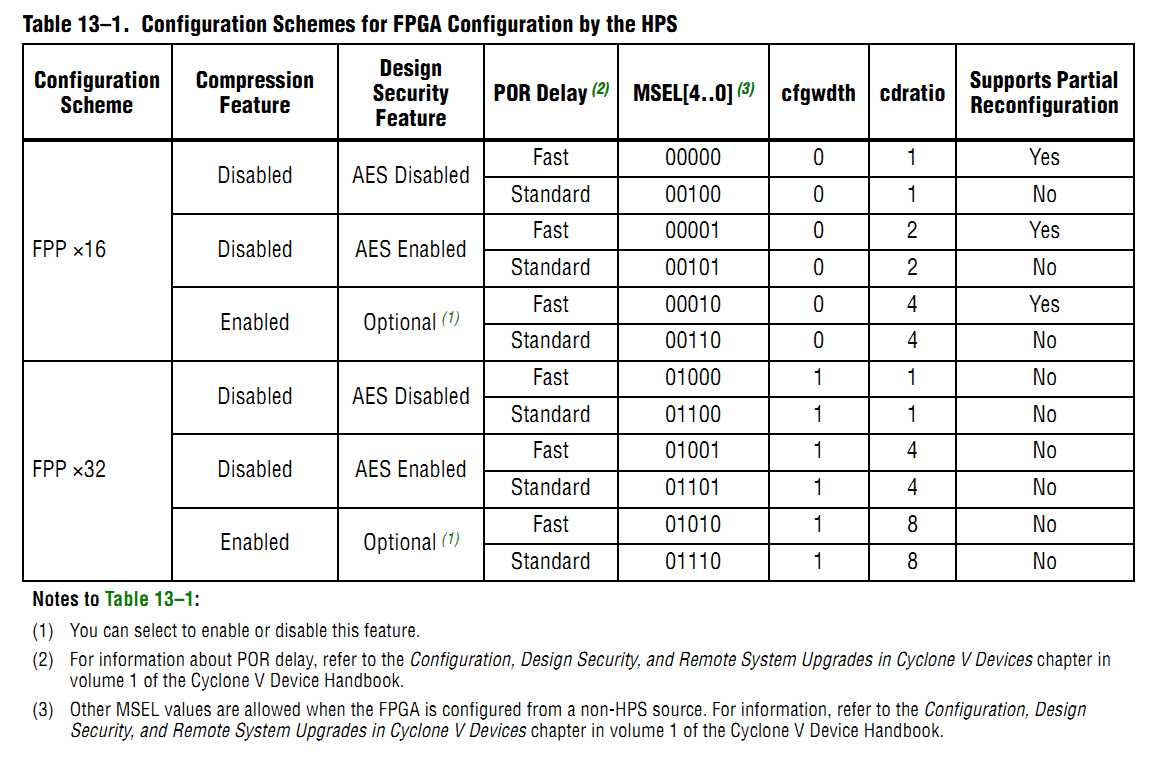

- Support CvP

- Config from QSPI - Boot HPS then load FPGA from HPS

- FPP is not supported on the Module with FPGA DDR memory

- Only bringing out 4 of the 8/16 data lines (B3A consumed internally)

- Will work on modules w/o FPGA DDR

- FPP IS used for booting from HPS!

- PS - 1bit @ 125MHz Max

- 10000

- 10001

- AS - 1bit or 4bit @ 100MHz Max

- 10010

- 10011

- CvP

- - set MSEL to boot peripheral image. Can be from a prom, or from the HPS preloader.

- Using the internal

- HPS FPGA Manager

- Design security is supported when using HPS FPGA configuration.

Resources¶

Configuration, Design Security, and Remote System Upgrades in Cyclone V Devices¶

http://www.altera.com/literature/hb/cyclone-v/cv_52007.pdf

Booting and Configuration¶

http://www.altera.com/literature/hb/cyclone-v/cv_5400A.pdf

Configuration via Protocol (CvP) Implementation in Altera FPGAs User Guide¶

Go to top