Utilizing QSPI NOR Memory¶

- Table of contents

- Utilizing QSPI NOR Memory

The MitySOM-5CSx family of modules are capable of booting, running from and/or accessing the on-board quad-spi NOR flash.

Depending on the specific module either 16MB, 32MB, 48MB or more QSPI NOR memory may be installed.

Note that for modules with greater than 16MB of NOR memory there will be two (2) individual memory chips installed. The first memory is always 16MB in size and uses the QSPI CS0 signal. If present the second memory will be 16MB or greater and uses the QSPI CS1 signal. The second memory cannot be used for booting the module but can be accessed from UBoot for the Kernel and beyond.

Memory Map¶

Please reference the following Wiki page for information on the required memory map for the first and second QSPI memory devices: U-Boot_on_the_MitySOM-5CSX

QSPI NOR Configuration Requirements¶

There are several items which all have to be addressed to successfully use the NOR flash:- The BSEL pins must be strapped correctly (set the boot mode to 0x6 (110b), see U-Boot_on_the_MitySOM-5CSX and Configuration wiki pages)

- The CSEL pins must be strapped to match your clock configuration.

- The MSEL pins must be strapped to match your desired FPGA configuration

- The preloader must be written to NOR flash at offset 0

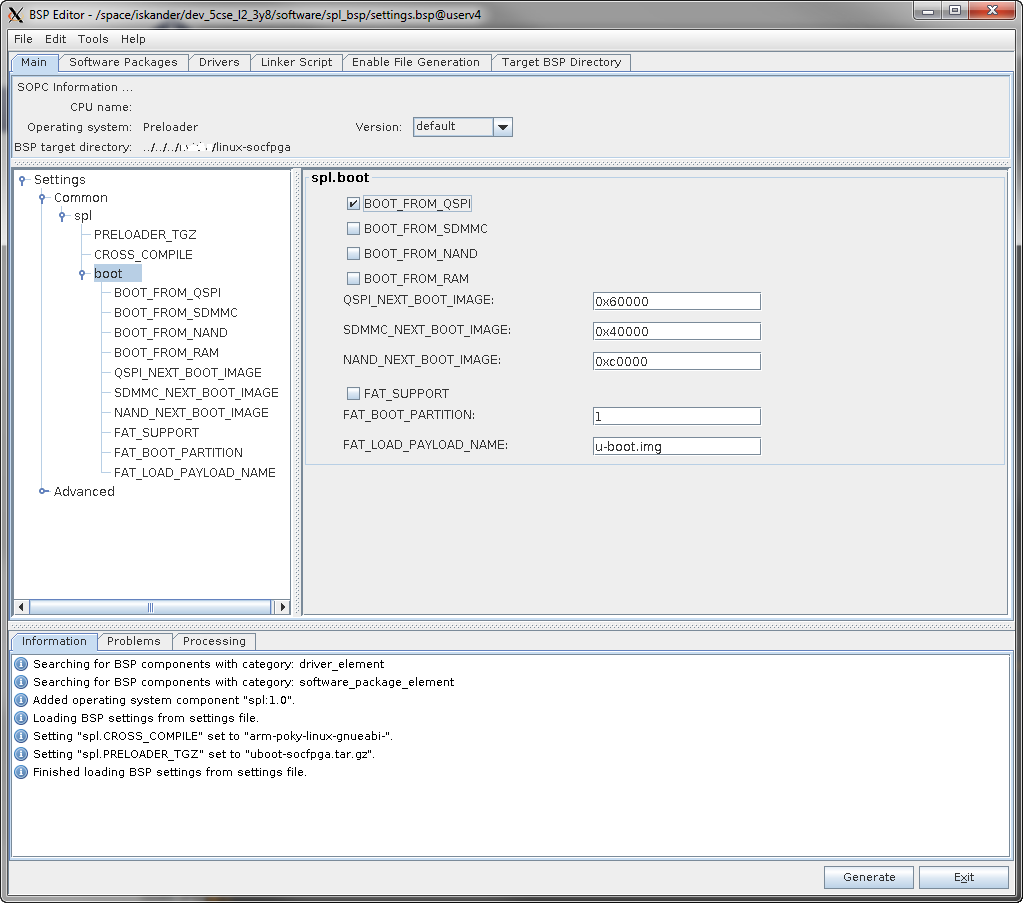

- The u-boot image must be written to NOR flash at the offset specified in the bsp-editor when you created the preloader ( see Building_u-Boot_and_Preloader ).

On modules with more than 1 QSPI NOR chip, the preloader and uboot must reside in the 1st (CS0) chip (which the 0 offset will get you)

Once you have loaded u-boot, you are free to complete system initialization in whatever means fits your design.

You can continue to boot and run from NOR using a RAM based filesystem (or flash-based filesystem such as JFFS or UBIFS).

QSPI Programming¶

Program QSPI NOR via UBoot¶

If you have a first stage boot device on your carrier board such as an SD card you can initially boot the preloader and UBoot from the SD card and then program the QSPI NOR from UBoot. This method allows you to access a number of peripherals (Ethernet, SD card, serial, etc.) for transfer of any application image file you wish to write to the QSPI NOR.

Sample instructions for writing to NOR memory from UBoot can be found on the U-Boot_on_the_MitySOM-5CSX wiki page.

Program QSPI NOR via JTAG¶

If the only boot medium you have is NOR flash, you will have to program the flash before being able to boot the module. To do this you will need to program BOTH the preloader and u-boot over jtag initially.

- Create a binary file (ie.

boot_image.bin) containing the preloader and u-boot.img files (at the correct offsets)

For example (following the flash layout shown in U-Boot_on_the_MitySOM-5CSX (i.e. QSPI_NEXT_BOOT_IMAGE = 0x60000):

This is the minimal set of things required to boot to uboot:# Create an image big enough for the preloader, uboot env, and u-boot dd if=/dev/zero bs=128k count=5 of=boot_image.bin # Copy in the preloader at 0x00000 dd if=preloader-mkpimage.bin of=boot_image.bin bs=256k count=1 conv=notrunc # Copy in the uboot env at 0x40000 dd if=ubootenv.bin of=boot_image.bin bs=128k count=1 seek=2 conv=notrunc # Copy in uboot at 0x60000 dd if=uboot-socfpga/u-boot.img of=boot_image.bin bs=128k seek=3 conv=notrunc

- Connect the USB blaster to HPS JTAG on the Drive PX board (J2)

- Run a Quartus Embedded Command Shell

- Run the quartus_hps command to download the blob

quartus_hps -c 1 --operation=P boot_image.bin

Note that the above quartus_hps command is using cable 1 (-c 1), this may need to change to match your local setup... run jtagconfig to determine the cable #

This will write the contents of boot_image.bin to the NOR flash at offset 0

Run quartus_hps --help for help on this command

NOTE: Programming over the JTAG can be quite slow.

QSPI NOR Access from Linux and/or Application¶

You can also access the QSPI NOR flash memory from within Linux and/or a Linux application with the MTD utilities.

To enable the QSPI MTD devices, the following kernel config options must be set- CONFIG_SPI_CADENCE_QSPI

- CONFIG_MTD_M25P80

- CONFIG_SPI_MASTER && CONFIG_MTD_SPI_NOR

Also, the QSPI partitions must be defined in the device tree (i.e. arch/arm/boot/dts/socfpga_mitysom5cs.dtsi - qspi: spi@ff705000 ...)

Go to top